At the 62nd ACM/IEEE Design Automation Conference (DAC) recently convened in San Francisco, a collaborative research effort between ShanghaiTech University and the Chinese University of Hong Kong, titled “LVM-MO: A Large Vision Model Pioneer on Full-Chip Mask Optimization,” earned a Nomination for Best Paper Award, marking the second consecutive year that ShanghaiTech’s research has been honored with this accolade at DAC. This showcases ShanghaiTech’s innovative prowess on the global EDA stage.

DAC, spotlighting cutting-edge advancements in electronic design automation (EDA), embedded systems, software, and silicon intellectual property, is a premier global event in the EDA field, attracting 1,862 paper submissions this year, with only 420 accepted. Among them, one paper received the Best Paper Award, and six were nominated for the Best Paper Award. Wu Yiwen, a 2023 PhD student, and Chen Yuyang, a 2022 master’s student, both from the School of Information Science and Technology (SIST), presented the research as co-first authors.

As the integrated circuit (IC) design and manufacturing industry enters the post-Moore era, optical proximity correction (OPC) for full-chip layouts, known as mask optimization, has become a critical process for semiconductor companies and foundries to enhance chip yield, reduce turnaround time, and lower costs. Meanwhile, advancements in artificial intelligence (AI) have opened disruptive opportunities in this industry.

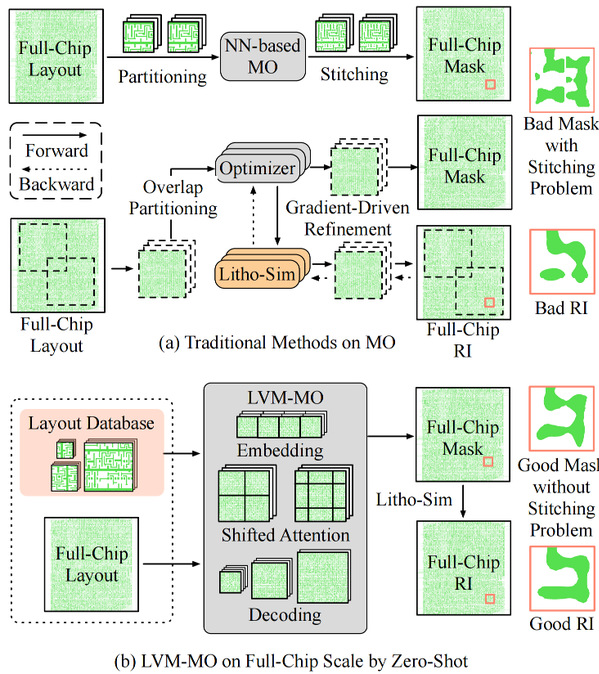

ShanghaiTech’s research team focused on improving mask optimization efficiency, pioneering the systematic application of large-scale vision models to full-chip mask optimization. They leveraged the graph feature extractor in a large vision model (LVM), precisely capturing geometric topology effects and circuit design rules in chip layouts, achieving comprehensive mask optimization for full-chip layouts. Stemming from a year-long effort to build a massive lithography dataset and carefully designed tasks, including layout geometry reconstruction and optical feature learning for multi-scale layout, the team’s innovation enabled their LVM to efficiently adapt to full-chip mask optimization workflows. Experiments demonstrated that the method outperforms state-of-the-art techniques in key metrics such as lithographic pattern fidelity, correction speed, and the ability to handle full-chip-scale layouts. Moreover, this research lays a robust theoretical and engineering foundation for applying large models to IC manufacturing and metrology.

“The motivation for this study was to address the inefficiencies and boundary continuity issues caused by traditional divide-and-conquer optimization methods in full-chip scenarios,” said Chen. “Drawing inspiration from large models in computer vision and tailoring them to computational lithography, we found that the strong generalization capabilities of LVM, combined with mechanisms like window attention, enable mask optimization for full-chip layouts. Ultimately, we proposed a novel approach using a LVM that understands the physical and chemical properties of optical imaging to tackle full-chip mask optimization.”

Wu added, “It’s an immense honor to represent ShanghaiTech and receive the Nomination for Best Paper Award at DAC for two consecutive years. This achievement would not have been possible without the university’s continuous investment in high-performance computing resources and the dedicated guidance from our professors in research and coursework.”

Luigi Capodieci, an EDA expert, CTO at Motivo, and SPIE Fellow, praised the work as “a highly forward-looking and engineering-valuable breakthrough.”

Figure 1: Group photo of the authors from ShanghaiTech (third from left: Chen Yuyang, third from right: Wu Yiwen).

Figure 2: Comparison of traditional mask optimization workflow versus the full-chip mask optimization workflow based on LVM.