传统光刻技术主导了当前的平面化工艺制造,但在10纳米以下三维结构加工中面临成本高、工艺复杂等挑战。自下而上组装纳米结构的方法被视为是可行的替代方案,但液相法主导的组装常因表面配体污染导致材料纯度不足,性能受限,且难以实现复杂三维结构的高分辨率器件的集成。近日,上海科技大学物质科学与技术学院冯继成课题组通过自主研发的法拉第3D打印技术,在高纯惰性气体环境中以“自下而上”的方式,实现了晶体管的可控制造。相关成果已发表于国际学术期刊Small。

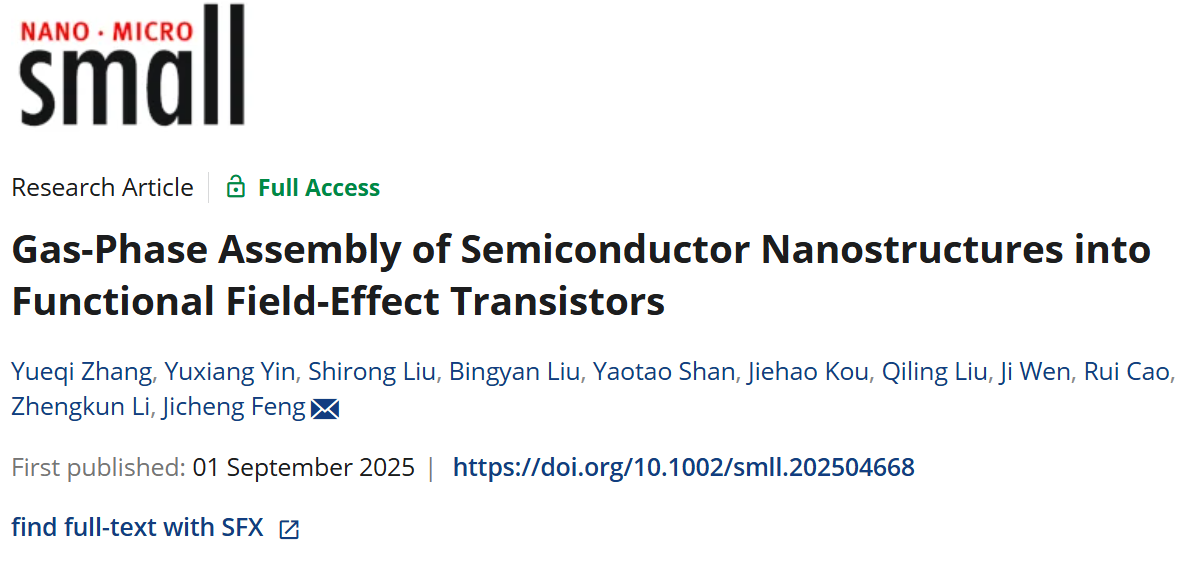

图1. 气相法制备的半导体纳米颗粒,结晶度高、分散性好

本工作首先在“人工闪电”等离子体环境中,成功制备出多种尺寸约5纳米的半导体材料,包括Si、Ge、ZnO、In₂O₃、InZnOₓ、GaAs和SiC等。该全干法工艺可有效避免配体污染,保障材料的高纯净度,尤其适用于对空气敏感的 GaAs、SiC 等材料。研究发现,纳米颗粒因超高表面原子比例而呈现类液滴的凝并行为,这一特性有助于在后续打印过程中实现融合生长,保障打印纳米结构的半导体性能。

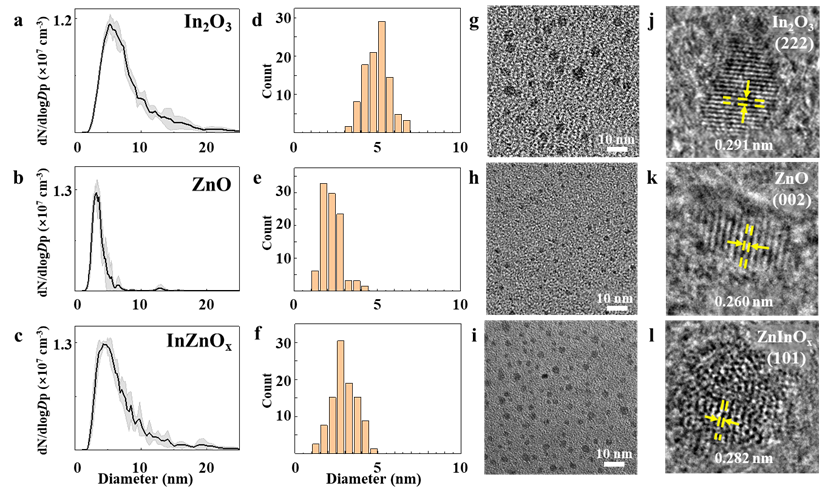

图2.3D打印的半导体纳米Fin及其复杂三维结构

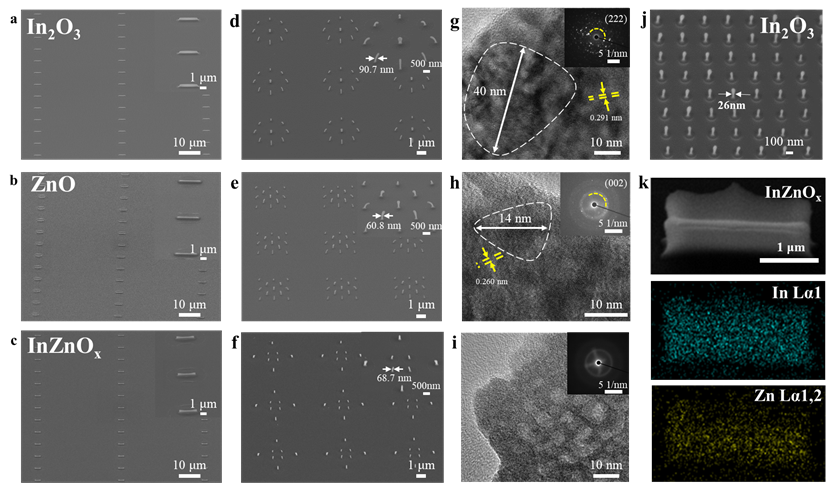

法拉第3D打印技术实现了材料属性与结构成型的解耦,能够打印出不同半导体材料但尺度一致的三维纳米结构,且这些结构仍可保持良好的本征半导体特性(图 2、图 3)。X射线光电子能谱(XPS)和光致发光(PL)光谱分析验证了打印结构的成分与光学性质。XPS与PL作为互补表征手段,为3D打印半导体纳米结构的本征属性提供了可靠依据。

图3. 3D打印半导体纳米结构材料属性

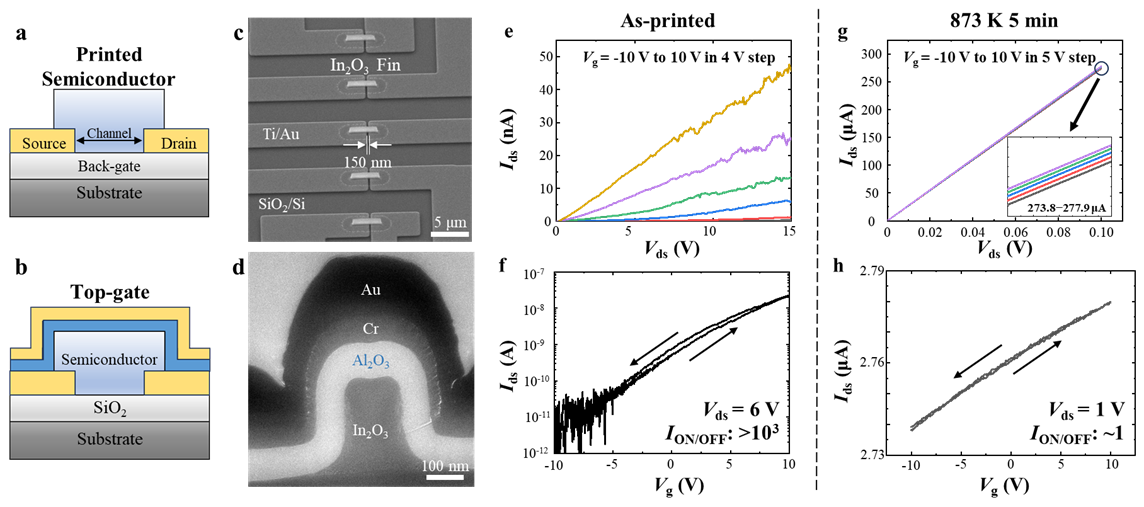

图4. 顶栅和底栅晶体管表征

研究进一步将打印出的氧化铟Fin结构作为沟道,集成到底栅和顶栅FinFET器件中。其中,顶栅控制的场效应晶体管(FET)表现出超过 1000 倍的开关比;经退火处理后,器件载流子迁移率提升至8.33 cm²·V⁻¹·s⁻¹。然而,热处理也导致载流子浓度过高,进而出现了“简并半导体”行为,使FET丧失了开关功能。为解决该问题,团队计划后续通过可控掺杂和尺寸优化进一步提升器件性能。

该研究展示了自下而上、原位打印技术在晶体管制造中的潜力。法拉第3D打印凭借其高空间自由度、纳米级分辨率和多材料原位切换能力,为三维芯片结构的可控制造提供了一条无需光刻的新路径。未来,冯继成课题组将继续探索掺杂调控、新结构设计及新材料体系,进一步提升半导体迁移率与晶体管开关性能,推动该技术在微纳器件领域实现更广泛的应用。

论文标题:Gas-Phase Assembly of Semiconductor Nanostructures into Functional Field-Effect Transistors

论文链接:https://onlinelibrary.wiley.com/doi/10.1002/smll.202504668

沪公网安备 31011502006855号

沪公网安备 31011502006855号