近日,第62届设计自动化国际会议(ACM/IEEE Design and Automation Conference,DAC)在美国旧金山召开。上海科技大学与香港中文大学合作研究成果“LVM-MO: A Large Vision Model Pioneer on Full-Chip Mask Optimization(利用视觉大模型实现全芯片尺寸级的掩膜优化)”荣获“最佳论文提名”。这是上海科技大学研究成果继2024年首次获得该项提名后,再次获此殊荣,在国际EDA舞台充分展示了上科大研究团队的创新能力。

设计自动化国际会议以EDA、嵌入式系统及软件和硅知识产权为主题,专注于EDA相关领域的最新方法和技术,是全球EDA领域的盛会。本届会议共收到投稿论文1862篇,最终录用420篇,其中仅1篇获评“最佳论文奖”、6篇入选“最佳论文奖提名”。上科大信息科学与技术学院2023级博士研究生邬一闻和2022级硕士研究生陈禹阳作为论文共同第一作者在大会上作成果汇报。

随着集成电路设计制造领域迈入后摩尔时代,全芯片尺寸版图的光学邻近效应修正,即掩膜优化,已成为半导体公司与晶圆代工厂提升芯片制造良率、削减周转时间并降低成本的关键环节。与此同时,AI技术的发展为该领域带来了颠覆性机遇。

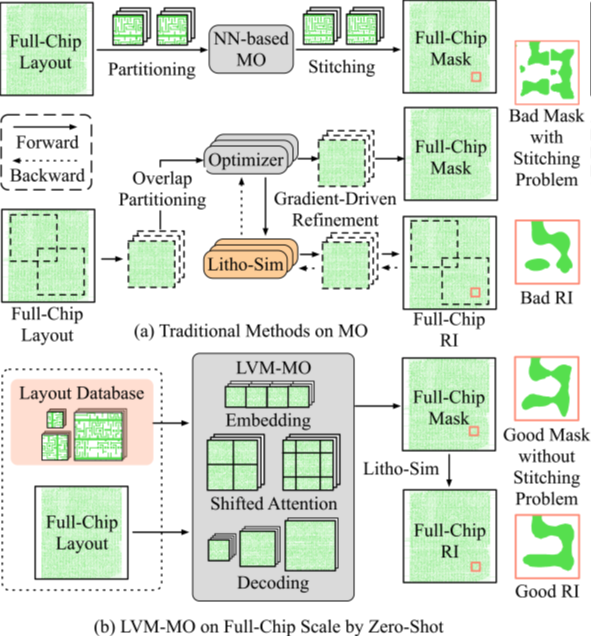

上科大研究团队聚焦提升掩膜优化效率,首次系统探索了大模型在全尺寸掩膜优化中的应用,提出了一种全新范式:结合“大规模光刻数据+大视觉基础模型+上下游任务协同”,利用大视觉基础模型配备的图特征提取器,精确感知大尺寸版图中的几何拓扑影响、电路设计规则,并巧妙融合了真实光刻过程中的光学成像物理与化学特性,实现全尺寸版图的掩膜优化。得益于研究团队历时一年多构建的大规模光刻数据集,以及精心设计的上下游任务(包括上游版图几何信息重建任务和下游多尺寸版图光学特征学习任务),团队构建的大视觉基础模型能够高效适配全芯片尺寸的掩膜优化流程。实验证明,在光刻图案保真度、修正速度以及处理全芯片规模版图的能力等多个关键维度上,该方法均优于当前最先进技术。此外,该研究也为大模型在集成电路制造、量测等领域的深入应用奠定了坚实的理论和工程基础。

“本研究的初衷,是为解决全芯片尺寸下传统优化方法使用分治所导致的优化效率低下及边界优化连续性问题。” 陈禹阳介绍,“参考基础大模型在计算机视觉领域的应用并结合计算光刻领域中的具体场景,我们发现可以利用视觉大模型的强泛化能力,结合窗口注意力等机制实现全尺寸芯片的掩膜优化。最终,我们提出了使用理解光学成像物理与化学特性的大视觉模型解决全芯片尺寸掩膜优化的新思路。”

邬一闻表示,“能够代表上海科技大学连续两届在DAC这类高水平的国际会议上获得最佳论文提名,我们感到非常荣幸。这一成果的产生离不开学校持续构建的高性能计算资源,还有导师们在科研工作及课程学习过程中给予的悉心指导。”

图1 论文作者合影(从右至左依次是何旭明、虞晶怡、邬一闻、陈禹阳、耿浩、吴涛)。信息学院虞晶怡教授和耿浩教授是论文的通讯作者,何旭明教授和吴涛教授是论文合作者。

图2 传统掩膜优化流程与基于大视觉模型的全芯片尺寸掩膜优化流程对比

EDA领域专家、Motivo公司首席技术官、SPIE Fellow Luigi Capodieci博士对这项成果给予了高度赞誉,称该工作是“极具前瞻性和工程价值的突破”。

图3 作者邬一闻在DAC 2025现场进行成果汇报

沪公网安备 31011502006855号

沪公网安备 31011502006855号